메모장

Single Pulser Circuit의 구현 본문

수업에서 프로젝트를 하다가 Pulser의 필요성을 느꼈다.

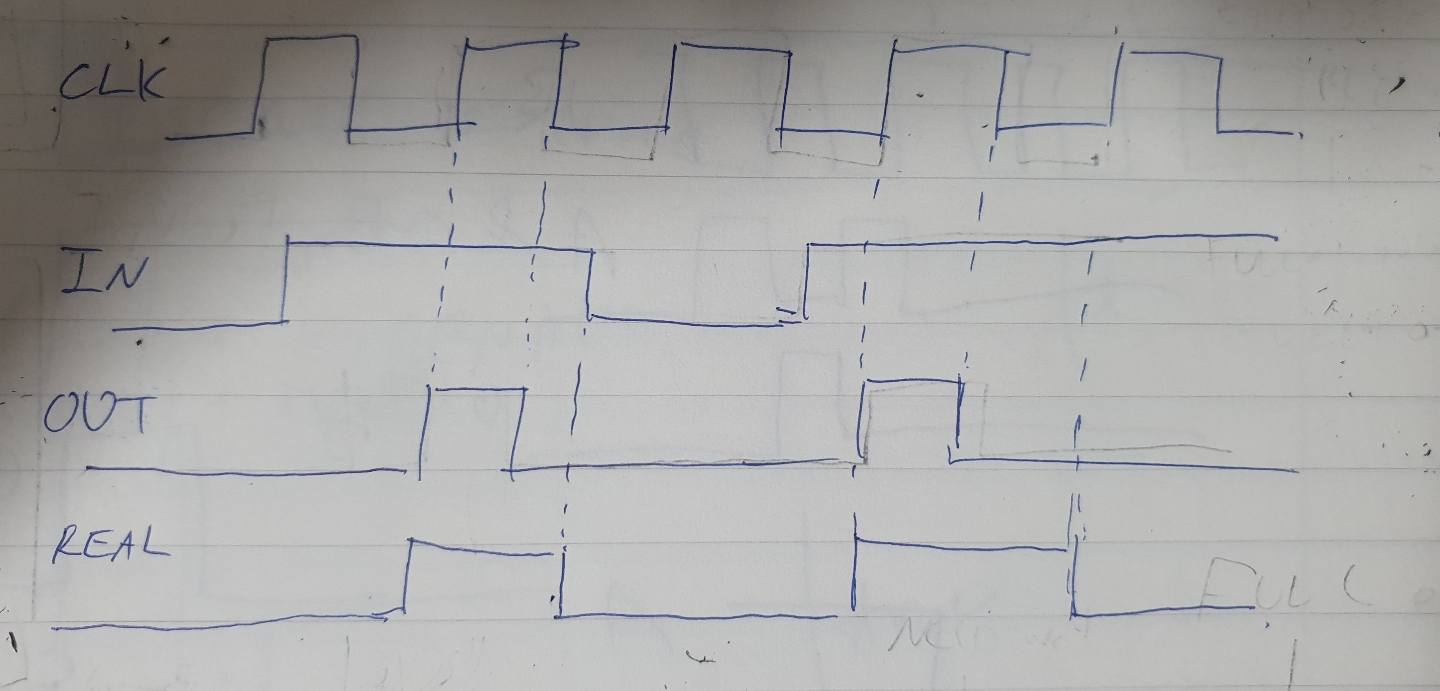

우리가 필요했던 Pulser는 입력이 0에서 1이 되는 순간(rising edge), 출력으로 클락과 동기화된 반 클락 길이(0보다 크고 1보다 작기만 하면 됨)의 1의 pulse를 출력하는 소자였다. 한마디로 다음의 기능을 하는 소자다.

조교님들께서 제공해주신 pulser는 debouncing을 위해 신호가 0에서 1이 들어오는 그 순간이 아닌, 그 다음 다음 클락에서 인식하여 완벽히 동기화되지 않아 사용할 수 없었고, 수정하려 해도 vhdl 파일이라 사용 금지였다.

우리가 구현을 비효율적으로 한 건지 모르겠지만 프로젝트에서 이러한 기능이 꼭 필요하였는데, 딱히 제공된 바도 없었고 이런 기능의 알려진 소자는 없었다. (그땐 구글링해도 못 찾았는데 single pulser라고 치니 내가 만든거와 똑같은 하나가 뜨기는 한다)

그래서 어떻게 만들까 고심하던 중 아래의 회로를 생각해냈다.

이러한 회로를 사용하면 Sout의 출력이 저 위 사진의 REAL과 같이 나오게 된다. 처음에 의도한 바와 약간은 다르지만 어차피 동기화되게 딱 한번만 이후의 FF에서 인식하면 되므로 이렇게 사용하였다.

클락 주기보다 적당히 긴 input에 대해서 output이 정확히 한 클락 길이라 그 다음 Rising Edge에 문제가 생길 수 있지만, Xilinx에서 사용한 모든 FF들은 정확하게 클락의 Rising Edge의 우극한의 데이터에 대해서 처리하기 때문에 프로젝트 내에서 큰 문제는 없었다.

그리고 왜인지 모르는데 Sin 신호에서 inverter를 통과한 신호가 입력되면 시뮬레이션 상으로 10ps만큼의 딜레이가 생기는 문제가 있었다. 인버터 두개를 통과하면 의도치 않은 딜레이가 생기는거 같은데, 때문에 인버터의 위치를 뒤바꾼 또다른 소자를 만들어서 사용하였다. 실제 회로에서는 확실히 이대로 사용하면 여러 문제가 있을 수 있을 것 같지만, FPGA는 ideal하고 소자들의 delay가 없게 optimize해주므로 잘 작동한 거 같다.

이를 응용하면 아래와 같이 입력 신호에 대해서 딱 두 클락만 1이 출력되는 신호도 만들 수 있다.

p(X)는 앞에 구현한 X를 입력으로 하는 펄스 출력이다. 맨위 사진의 REAL의 경우가 아닌 OUT의 경우일 때라 실제 출력은 약간 다르긴 하지만, 두클락동안 1인건 변함이 없다. 그러나 이 논리식 (p(A)or p(~p(A)))로 소자를 만든 결과 작동하지 않아 이유를 찾다가 위에 서술한 인버터 딜레이 때문임을 깨달았고, 얼마 후에 이 기능이 필요없다고 판단되어 사용하지 않았다.